Timing Constraints

Input- and Output Delays

In the last blog, primitive and generated clock constraints were introduced. These timing constraints are needed to do a basic clock constraining of the clocks, which are used inside the FPGA and especially for FPGA internal static timing paths. But the internal paths inside the FPGA are not the only paths which has to be constrained in a complete system. In most of the FPGA designs, we have input and output interfaces, where the upstream device is generating data, which is received by an input interface, while the downstream device is receiving data which is generated by an output interface of the FPGA.

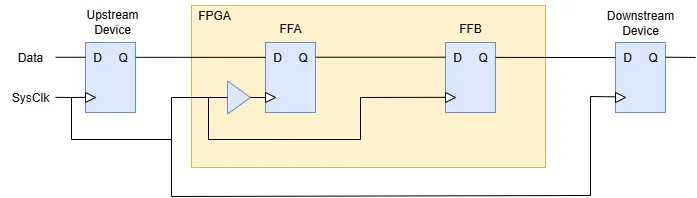

If the interface of the input or the output interface is a synchronous interface, it is important to define additional constraints there. In the following picture, a simple example is shown, where the FPGA has system synchronous interfaces at the input and at the output of the FPGA.

Figure 1: FPGA with system synchronous interfaces

This means, that there is for example a clock oscillator, which provides the clock to the upstream device, the FPGA, and the downstream device. In this case, all the three components of the system are running with the same clock.

If we only define a primitive clock constraint for the Sysclk, only the internal static timing path from FFA to FFB is properly constrained. The delay of the data connection from FFA to FFB is known and calculated by the tool, because this path is an internal path inside the FPGA. But what is not known to the tool, is the delay of the data connection from the upstream device to FFA and the delay from FFB to the downstream device. These paths are external to the FPGA and cannot be known by the tool. The user must constrain them and define the delay, so that the STA is calculating with this information.

In this case, the two external paths must be defined by using input and output delay constraints. The definitions of these timing constraints are the following:

Input delay constraint:

set_input_delay –clock <clock_name> <delay> <objects>

Output delay constraint:

set_output_delay –clock <clock_name> <delay> <objects>

The constraints are used to define the delay in ns on the data line, regarding the clock which is used for the specific paths.

If you would like to deepen your Timing expertise, join our »Compact Timing Constraints and Analysis« training, and take your skills to the next level.