Timing Constraints

Exceptions

In the first two Blogs, basic clock constraints and input and output constraints were presented. To fully constrain a FPGA design, there is one important topic missing: Timing exceptions.

Exception constrains are used, to define, that there a specific timing paths, that should not be analysed by the Static Timing Analysis (STA) in a typical way. This means, that there will be no setup and hold time analysis on the excluded paths, compared to static timing paths without exceptions. In almost every FPGA design, there is a need to define exceptions because of different reasons. The most popular reason is a Clock Domain Crossing (CDC).

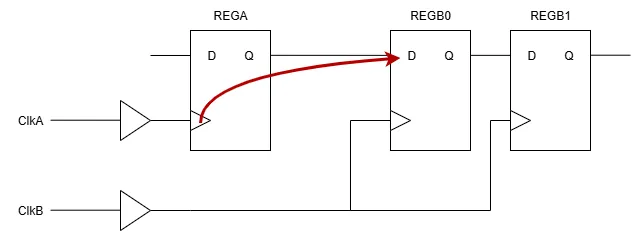

In the following example, there is a clock domain crossing path from ClkA to ClkB:

Figure 1: Example of timing constraints exceptions

We assume, that for both clocks, there are already primary clock constraints defined. Whenever clock constraints are defined on specific clocks, the timing for all existing paths is calculated. This is also true for paths between elements from different clocks domains. Whenever there are CDC paths in a design, they must be synchronized. In addition to that, exceptions must be defined.

A typical exception constraint which can be defined, is the false path constraint:

set_false_path <path_enumeration> <check_type>

This constraint is used to fully ignore a path in terms of timing. In this example, the constraint can be defined in the following way:

set_false_path –from [get_cells REGA] -to [get_cells REGB0]

There are more cases where the FPGA designer needs to support the tool (STA) in terms of defining exceptions. Several other exceptions exist for other different use cases. In our training courses, we teach attendees where exceptions are needed and which exceptions must be used. Other than that, useful reports are shown, which help to identify where exceptions are needed or if the timing constraints created are complete in general.

If you would like to deepen your Timing expertise, join our »Compact Timing Constraints and Analysis« training, and take your skills to the next level.