Independent Verification & Validation

Requirements-based testing, deliberately not by IP-designers

Description

Independent verification against requirements is a valuable method to increase product safety and to prevent failures at a late and costly project state. For projects dealing with functional safety requirements, independent verification by a team of experts can even be a requirement for the development process.

Methodology

Typically, designers of IP blocks described in VHDL or block design apply simulation of the code to check correctness. However, designers tend to test their understanding of their own code by simulation. While simulation by designers can be extremely useful to prevent errors, formally independent verification against the actual requirements by verification experts can complement and improve designs dramatically.

Independent verifiers at PLC2 deliberately ignore the IP design and use the requirements formulation as input to test cases and test benches. They use code coverage as guidance to improve test suites and use error injection to stimulate paths that designers coded but perhaps never simulated. PLC2 verifiers typically use established frameworks such as OSVVM to build test harnesses and regression suites with automated test report outputs.

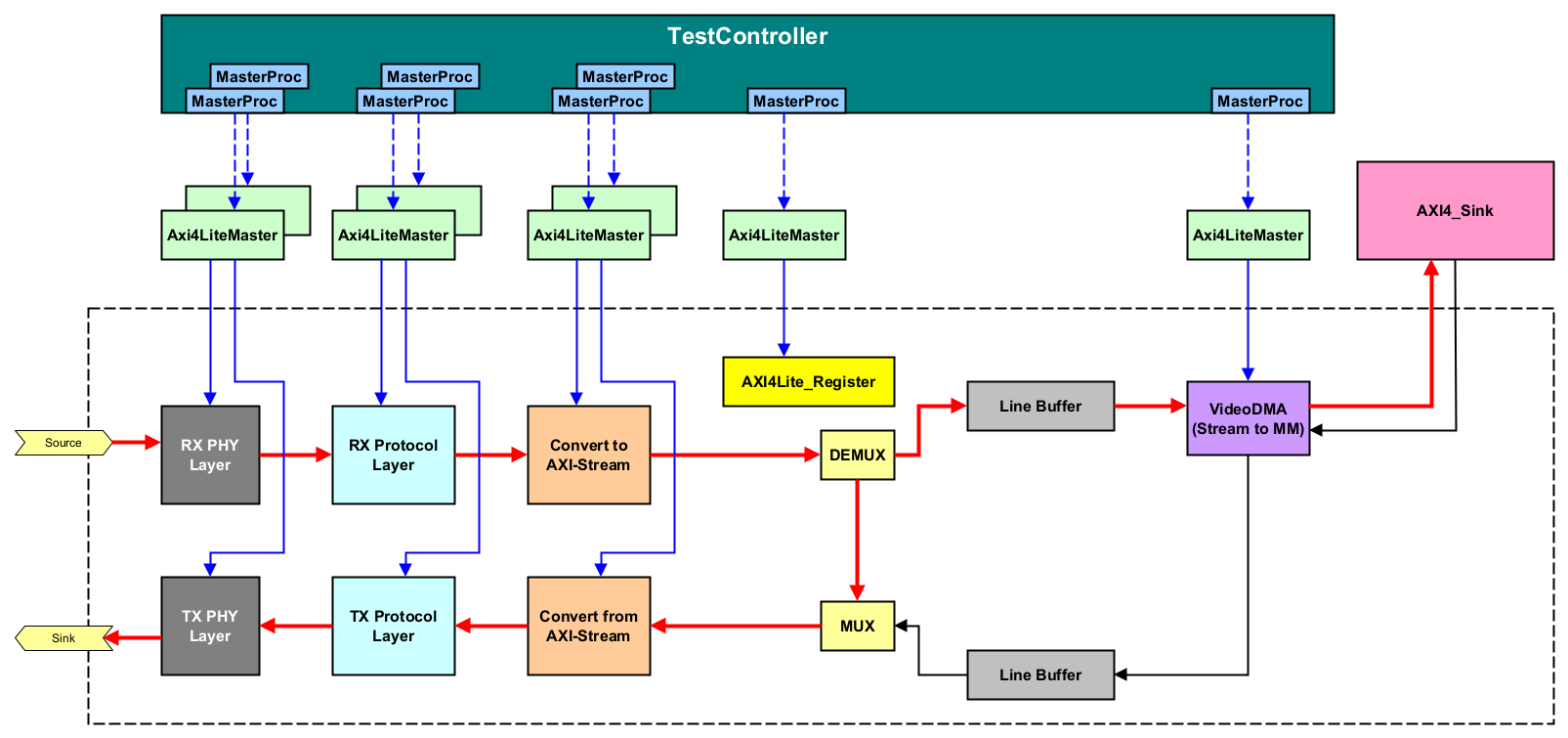

Generic test harness for video processing pipeline

Due to the extreme cost of ASIC tapeouts, independent verification can also be extremely useful and overall cost saving for ASIC designs.

Conclusion

Independent verification against the requirements can significantly contribute to the development process for products or applications with functional safety requirements. It can also reduce overall product development cost by systematic guidance through code coverage and application of well established frameworks such as OSVVM to build and maintain regression test suites.