FPGA Toolchain Reports

Ignoring them can cause serious unreliabilities

Description

FPGA-related toolchains such as Vivado provide a valuable set of report logs during processing stages. Unfortunately, their value for making a design robust and safe is often underestimated. For applications with functional safety requirements their proper analysis, application of correcting actions and stating justifications are often a must.

Methodology

FPGA projects utilizing programmable logic are typically described as block designs and / or VHDL. The process to generate a bitfile involves synthesis and implementation for the target device with a constrained pinout and surrounding peripherals. During these process steps toolchains such as Vivado™ generate synthesis reports, implementation reports, timing reports, Clock Domain Crossing (CDC) reports, power estimations, and more.

The following are example warnings from a synthesis report:

WARNING: [synth 8-327] inferring latch for variable ‘cs1_reg’

[C:/PLC2/USE_CASES/vhdl_wanrnings/example1/project_1.srcs/sources_1/new/top.vhd:42]

WARNING: [synth 8-327] inferring latch for variable ‘cs2_reg’

[C:/PLC2/USE_CASES/vhdl_wanrnings/example1/project_1.srcs/sources_1/new/top.vhd:43]

Typical synthesis warnings indicating an insufficient description in VHDL

The synthesis of latches is in most cases undesired and an indication of an incomplete VHDL description that should be improved to obtain a safe design.

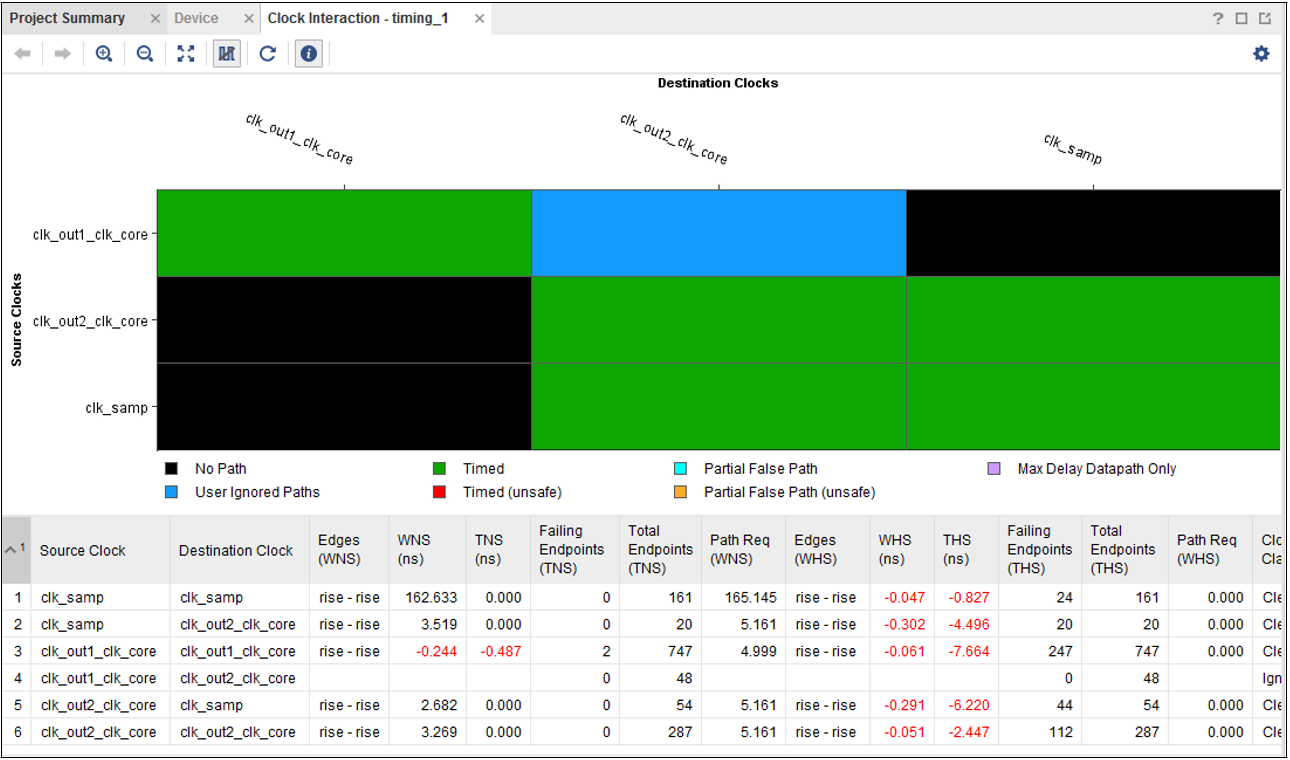

Another example is the clock interaction report below, generated by the Vivado™ toolchain in the CDC report to support experts in a systematic fashion:

Figure 1: Clock interaction report with unsafe clock domain crossing depicted in red

The matrix type visualization shows dependencies in both directions and color coding informs about potentially safe or unsafe implementation.

The log files often contain hundreds or even thousands of valuable information, warning, and error messages, but many designers simply ignore them. Problems often arise at a late project stage, when FPGA resource utilization reaches limits or product stability and repeatability testing over temperature is performed in a systematic manner.

PLC2 supports customers with reviews of the above reports, the generation or reviews of timing constraints, insertion of proper clock domain crossings, the corrections to be applied to VHDL code so that warning / error messages vanish, or, if certain messages are real but can be deliberately accepted, by writing the proper expert justifications to why a message can be accepted. For safety requirements on pinout (e.g. related to bank utilization or proper minimum distance between balls or pins), PLC2 also assists with the Isolation Design Flow (IDF). When power estimations are required for mechanical cooling concepts or plausibility checks against real-world tests, PLC2 assists with the tooling.

Typical results of the process are correctness by design where testing is an insufficient validation method and reliable and safe products for our customers. The independent documentation PLC2 provides additional evidence of a properly performed development process.

Conclusion

Report files generated by FPGA toolchains are too often ignored by designers, resulting in additional project costs at later stages. PLC2’s experts assist customers with reviews, proper interpretation, corrective actions, and documented evidence to ensure safe, robust, and reliable designs.